لینک پرداخت و دانلود در "پایین مطلب"

فرمت فایل: word (قابل ویرایش و آماده پرینت)

تعداد صفحات:16

واحد محاسباتی، منطقی و شیفت (ALU)

در کامپیوتر، به جای اجرای ریز عملیات بر روی هر ثبات، معمولاً یک سری ثبات به یک واحد مشترک محاسباتی، منطقی و شیفت ALU متصل میگردند. برای اجرای یک ریز عملیات، محتوای ثبات بخصوصی در ورودی ALU مشترک قرار میگیرد. واحد ALU عملیات مربوط را انجام میدهد، و نتیجه به ثبات موردنظر منتقل یشود. چون ALU یک مدار ترکیبی است، بنابراین، انتقال اطلاعات از ثبات منبع، به ALU و وارد کردن نتیجه به ثبات مقصد، در یک پریود پالس ساعت انجام میشود.

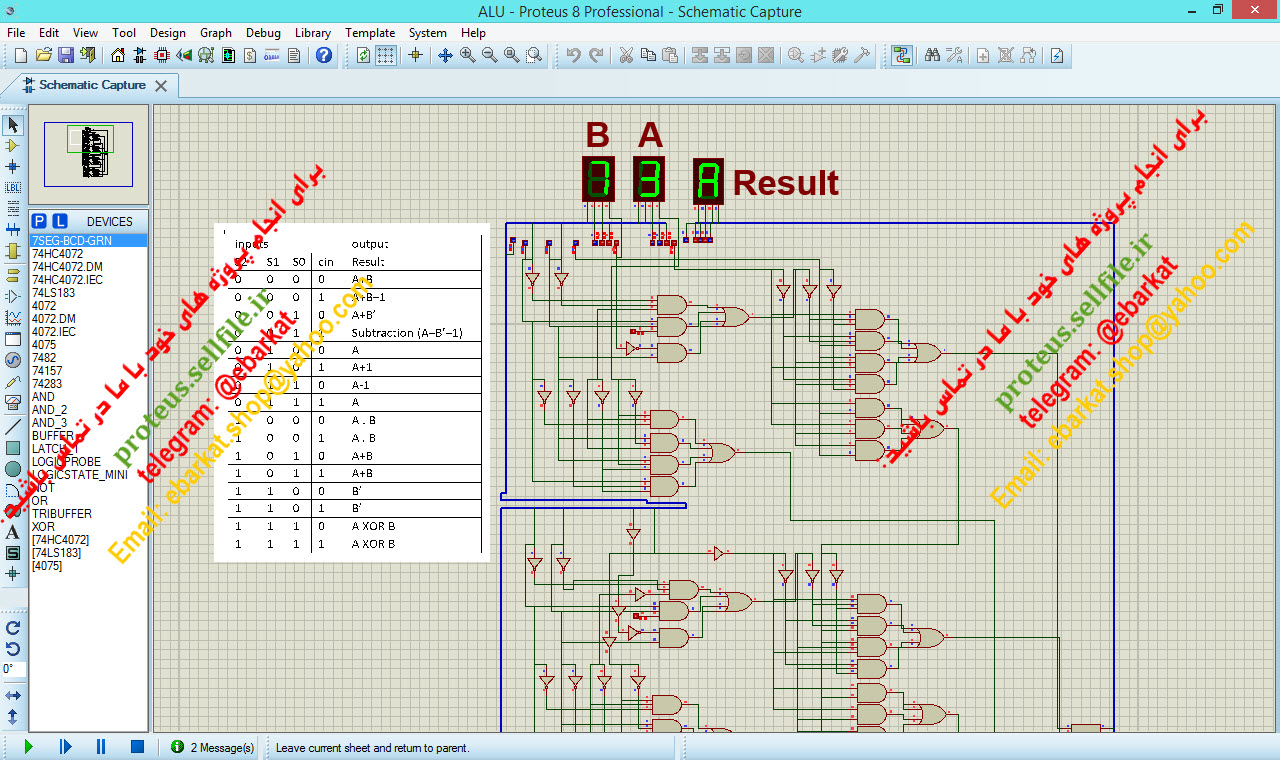

مدار محاسباتی

ریز عملیات ریاضی جدول (4-3) را می توان در یک مدار محاسباتی انجام داد. مبنای اولیه این مدار محاسباتی جمع کننده است که با کنترل اطلاعات ورودی به این جمع کننده، میتوان عملیات مختلف ریاضی را انجام داد.

مدار شکل 2 یک مدار محاسباتی چهار بیتی را نشان میدهد. این مدار دارای 4 جمع کننده کامل FA و چهار مالتیپلکسر برای انتخاب عملیات مختلف میباشد. مدار مذکور دارای چهار بیت ورودی A است که مستقیماً به ورودی های X جمع کننده ها وارد میشود و چهار بیت عدد B ، و مکمل آنها نیز به ورودی های 0 و 1 مالتیپلکسرها متصل شده است. در ورودی دیگر مالتیپلکسرها مقادیر 0 و 1 قرار داده شده است و خروجی های مالتیپلکسرها نیز به ورودی Y جمع کننده ها اتصال دارد. چهار مالتیپلکسر مذکور توسط دو بیت انتخاب S1S0 کنترل میشوند. بیت نقلی Cin ، به ورودی کوچکترین بیت جمع کننده متصل گردیده و بقیه بیت های نقلی خروجی جمع کننده ها، به ورودی بیت های نقلی جمع

کننده بعدی، وصل شده است.

مقاله درباره مدارهای ALU